一年一度的瑞士信貸科技會議 (Credit Suisse technology conference) 上 ,Intel (INTC.US) 的執行長羅伯特.斯萬對於生產的困境以及下一步的規畫做了說明,FinSight 整理他的發言並檢視行業發展,更加確認台積電在先進製程的領先地位。

Intel 生產遇到困難的原因?

Intel 的 CPU 處理器缺貨導致 PC 出貨量受到影響,甚至日前罕見地為此在官網上致歉。Intel 執行長在瑞士信貸科技會議上針對缺貨提出說明,主要有三點:

- CPU 需求比預期的強勁:

原本預估成長 10%,但實際上是 21%,超出預期許多。 - 手機數據機晶片吃掉產能:

Intel 在手機數據晶片市佔率高且希望自製,現在已經將這塊業務切給蘋果。 - 高階製程進度延遲:

暫緩了 10 奈米桌上型處理器的推出,因此為了提高既有 14 奈米的效能,必須增加處理器的核心數,晶片尺寸也要越來越大。

其實主要原因還是高階製程進度延遲,10 奈米製程因良率而遲遲無法推出,在更高階產品產能無法開出的情況下,只好在 14 奈米產品增加電晶體讓晶片尺寸變大, 以提高效能。這樣的資本投入讓公司資源錯置,公司應該要把研發能量投入到未來的新製程,否則當對手在新製程推出功耗更低、效能更高的產品時,14 奈米產品又得增加晶片尺寸因應?

關鍵:製程要按步就班,每次推進一小步。

公司提到過去摩爾定律是每 18 個月電晶體數量變 2 倍,但是 Intel 的 22 奈米到 14 奈米,處理器上的電晶體數量變 2.4 倍;而 14 奈米到 10 奈米則計畫變 2.7 倍。因追求的標準太高,導致問題也不斷浮現。每個製程升級幅度過大 (微縮超過 1 倍),導致良率跟不上,良率差讓製程延後又會疊加更多的資本支出,使企業獲利下滑、進而排擠更新製程的資本支出,就會在產能與技術進程上落後。

越想要彎道超車,反而在良率上就很容易出問題。反觀台積電 (2330.TW) 則是每一段製程都小幅更新,在每一個版本中間都還有優化版,每個大節點的前後都有鋪陳與優化版。

從 7 奈米製程看台積電佈局就相當明顯,一開始用重複曝光做 10 奈米,再用重複曝光做 7 奈米,接著用 EUV 版本替代 3 ~ 4 層光罩成為 7 + 奈米製程 ,再將 EUV 導入 5 奈米。台積電的每次製程的更新只專注優化一樣技術,然後每年推出小改版,確保每個改版的良率夠高之後再往前走。

台積電本身的製程地位領先,讓他更有空間可以逐步優化,這樣的過程反而讓製程推新更快。高良率讓他能順利量產取得營收,營收成長也足以支撐資本支出所增加的折舊,創造出來的獲利與現金流又可以持續投入最新製程的研發支出,創造領先優勢。這樣的模式,讓台積電在製程的進度上取得領先,目前只有台積電有辦法做到導入 EUV 的量產,因此各大廠都競相下單台積電的 5 奈米與 7 奈米製程,以順利推出更高階產品。

Intel 執行長羅伯特.斯萬 :「放下 CPU 市佔九成的執著,放眼 30% 半導體市場。」

會這樣說,其實背後代表了兩件事:

- 先進製程落後,使 AMD (AMD.US) 持續吃掉 CPU 市佔。

- 證實異質整合立體封裝,在高速運算晶片中的重要性。

先進製程落後,使 AMD 持續吃掉 CPU 市佔

- Intel 並不是沒有布局 CPU 之外的半導體市場,而是沒有做得很好:

從這幾年 Intel 的布局可以看到,他藉由併購來加強做不好的產品,像是 2015 年做 FPGA 的 Altera (ALTR.US)、2017 年做車用晶片的 Mobileye。不過 HPC (高速運算) 市場更強調如何把產品綜合在一起,而非單獨運行。 - CPU 當然還是重要,但AMD有先進製程支援後,真的追上來了:

競爭對手 AMD 採用台積電的領先製程後,開始推出效能可與之競爭的產品,Intel 的市佔自然會被挑戰。更何況 Intel 今年推的是低耗能 10 奈米晶片,真正高效能的 PC 和 Server 產品要等 2020 才能推出,整整落後台積電一年。

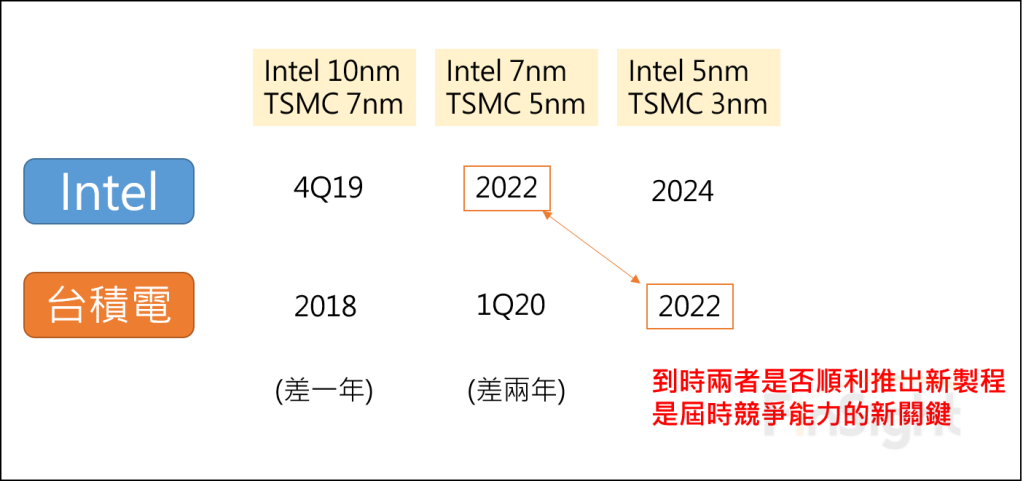

AMD 的 5 奈米晶片可能 2020 就要推出,而 Intel 約當同等級的 7 奈米製程目前規劃 2022 年才推出,但參考 10 奈米良率拉不起來的經驗,也是讓人擔心會延遲。同時台積電 3 奈米預計在 2022 年推出 (約當 Intel 5奈米等級) ,屆時 Intel 若還無法推出 7 奈米的產品,兩者將正式有兩個世代的差距。到時候 Intel會更痛苦,甚至需要認真思考交給台積電的代工。

FinSight 認為:2022 年是 Intel 是否真正落後兩代的關鍵時間!

圖一、台積電與 Intel 各製程預估推出時程

證實異質整合立體封裝在高速運算晶片中的重要性

要持續提升晶片效能在技術上有三個方向,分別是:

- 製程微縮:導入 EUV 後到 3 奈米沒問題,1 ~ 2 奈米還有機會嘗試,但小於 1 奈米幾乎是不可能。

- 立體封裝:利用三維堆疊的方式,在有限的空間提高效能,甚至進一步做到異質整合將多個不同性質的元件一起封裝。

- 新材料:強調更高頻材料的速度。

圖二、提升晶片效能的三個技術方向

異質整合是將不同性質的晶片,採用系統級的立體封裝技術整合再一起,可以增加效能並減少功耗。台積電的客戶在 7 奈米後的高階製程,有半數以上採用台積電的晶圓級立體封裝。搭配 Intel 的說法,也代表了半導體不是只有追求微縮,異質整合也很重要。

然而異質整合需要強大的整合能力,參考 Intel 過去其他產品的生產經驗,與 CPU 的成功相比顯得差強人意。雖然藉由併購取得了其他產品的技術,但像是 Mobileye 明年會從 28 奈米跳至台積電的 7 奈米。Altera 的 FPGA 也在被 Intel 收購之後,因沒有推出搭配先進製程的商品,導致市占大幅被 Xilinx (XLNX.US) 搶佔。加上沒有 GPU 成功的商品經驗。因此 Intel 在晶圓製造這塊,可以說只有 CPU 能發揮戰力,想要做到跨晶片的異質整合封裝,優勢絕對不如替所有廠商服務的台積電強。反觀台積電,封裝營收佔比已經近 10%,且持續推出立體封裝的優化版,這使 Intel 追趕難度更高。

圖三、立體封裝分類

結論:持續看好台積電的先進製程領先,並看好 AMD 持續增加市佔。

Intel 本次的論壇發言,透露出 Intel 在先進製程的困局與異質整合立體封裝的重要性,更顯現了台積電競爭優勢的強大。台積電的客戶也將藉由台積電的製程領先能力,推出更好的新產品,以搶攻對手的市佔。因此持續看好「台積電大聯盟」取得市佔。以台積電的地位來看,在半導體中的評價,長線勢必持續提高。

免責聲明:本文章內容僅供投資人參考,無任何推薦與買賣邀約之情事,投資人應獨立審慎判斷,自負買賣風險謹慎投資,本網站不負任何法律責任。

喜歡我們的文章嗎?歡迎追蹤我們的臉書粉絲團,我們會持續提供更多產業趨勢的分析唷。